RISC-V CPU Project for Imperial EIE 2023/24

Adam El Jaafari, Archisha Garg, Dimitris Alexopoulos, Toby Browne

The following goals were reached:

- Single-cycle CPU tag: single_cycle

- Pipelined CPU with hazard detection tag: pipelined_with_hazard

- CPU with cache tag: cache_only

- Pipelined CPU with hazard detection and caching tag: cache_pipeline_v2

- Full RV32I instruction set support (except

AUIPC,FENCE,FENCI.I,SCALL,SBREAK,RDCYCLE,RDCYCLEH,RDTIME,RDTIMEH,RDINSTRET,RDINSTRETH) - Fully pipelined with hazard detection and direct mapped cache

- 1024 bytes of cache

- 4096 bytes of instruction memory

- 131072 bytes of data memory

- 1 I/O (output) register

- 2 memory mapped I/O (input) ports

Key: o = Main Contributor; v = Co-Author

| Task | Files | Adam | Archisha | Dimitris | Toby |

|---|---|---|---|---|---|

| F1 Program | f1.s, f1_tb.cpp |

o | |||

| Program Counter | pc.sv |

o | |||

| Instruction Memory | instrmem.sv |

o | v | ||

| Control Unit | cu.sv |

v | o | o | v |

| ALU | alu.sv |

o | |||

| Sign Extend | se.sv |

o | |||

| Data Memory | datamem.sv |

o | |||

| Top Level | cpu.sv |

o | o | ||

| Pipeline Registers | fetchff.sv, executeff.sv, memoryff.sv, decodeff.sv |

o | o | ||

| Hazard Unit | hazard.sv |

o | v | ||

| Cache | cache.sv |

o | o |

This is the directory structure that was used for the project.

| Directory | Use |

|---|---|

rtl |

SystemVerilog modules |

test |

F1 lights program and testbench |

tb |

Testbenches and test programs/data |

doc |

Documentation and reports |

doc/images |

Documentation images |

These are some files which are important for building/using the project.

| File | Description |

|---|---|

tb/cpu.sh |

Build script for the CPU testbench |

test/f1.sh |

Build script for the CPU testbench |

tb/pdf.hex |

Reference program binary |

tb/gaussian.mem, tb/triangle.mem, tb/noisy.mem, tb/sine.mem |

Reference program data |

In order to build the project once must follow the following instructions.

Firstly the correct program has to be loaded in the instruction memory.

The following lines must be modified in rtl/instrmem.sv.

In order to run the F1 lights program, it can be left as.

To test the reference program, $readmemh("../test/f1.hex", mem_array) must be changed to $readmemh("../tb/pdf.hex", mem_array).

To change the type of signal used in the reference program the following lines need to be changed in the data memory.

The line $readmemh("../tb/gaussian.mem", mem_array, 'h10000) must be changed.

The path ../tb/gaussian.mem needs to be changed to point to the file you want to use, e.g. ../tb/triangle.mem

After the memory has been configured the following commands need to be ran.

Before running ensure cwd (current working directory) is the root of the repository.

cd tb

./cpu.shThe trace can be viewed by running:

gtkwave cpu.vcdBefore running ensure cwd (current working directory) is the root of the repository.

cd test

./f1.shThe trace can be viewed by running:

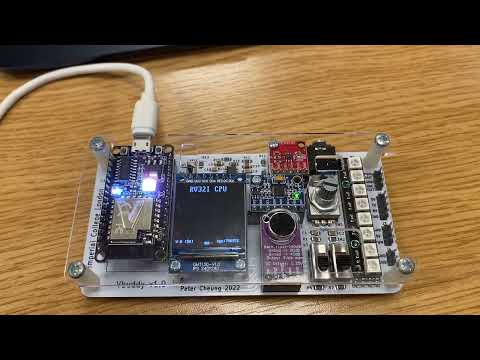

gtkwave cpu.vcdBelow you can see videos of VBuddy running the reference programme and the F1 lights program, as well as the corresponding traces. The images are linked to videos showing the operation so please click them.

The project has been open-source licensed under a BSD-3-Clause license for educational purposes.

This does not inlcude the reference program tb/pdf.s and it's associated *.mem files, as well as the tb/vbuddy.cpp file.

Copyright for the previously mentioned files is attributed to Peter Y. K. Cheung and thus the license does not apply to them.